EUV 공정 기반 7나노 이하 칩에 적층 기술 적용 성공

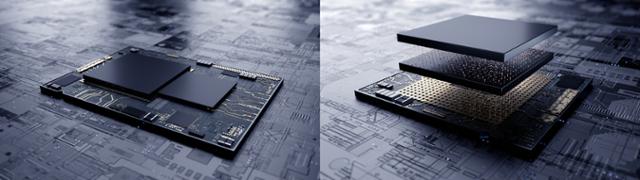

삼성전자가 업계 최초로 극자외선(EUV) 초미세공정 기반 시스템반도체에 적층 기술을 적용한 시제품 생산에 성공했다고 13일 밝혔다. 시스템반도체 주요 부분을 나란히 평면 설계하는 기존 방식(왼쪽 사진)과 달리 3차원 칩 적층 기술 '엑스큐브'를 적용(오른쪽 사진)해 전체 칩 면적을 줄이고 성능을 높였다. 삼성전자 제공

삼성전자가 업계 최초로 극자외선(EUV) 초미세공정 기반 시스템반도체에 적층 기술을 적용한 시제품 생산에 성공했다. EUV로 반도체 회로를 폭 7나노미터(㎚, 10억분의 1m) 이하로 세밀하게 새기는 것을 넘어 칩을 쌓아올리는 기술을 확보한 것으로, 한층 좁은 면적에 고성능을 구현할 수 있게 됐다. 삼성전자는 팹리스(반도체 설계 전문) 고객 의뢰를 받으면 바로 제품을 개발·양산할 수 있는 채비도 마쳐 대만 TSMC와의 파운드리(반도체 위탁생산) 경합에서 경쟁력을 확보했다.

13일 삼성전자에 따르면 회사 디바이스솔루션(DS)부문 파운드리사업부는 최근 EUV 기반 7나노 칩에 3차원 적층 패키지 기술 '엑스큐브(X-Cube)'를 적용한 테스트칩(시제품)을 생산했다. 엑스큐브는 웨이퍼(반도체 원재료)에 회로를 새긴 상태의 칩을 여러 개 얇게 쌓아 하나의 반도체로 만드는 기술이다.

시스템반도체는 정보를 처리하는 로직 부분과 저장을 담당하는 캐시메모리 부분으로 나뉘는데, 통상 같은 기판에 두 부분을 병렬 배치하는 형태로 설계된다. 반면 엑스큐브는 로직 칩과 캐시메모리 칩을 따로 만든 뒤 직렬 배치해 전체 칩 면적을 줄이고 자유로운 설계를 가능하게 한다. 회사 관계자는 "시스템반도체 일반 공정에 적용되던 적층 방식을 7나노 이하 초미세공정에 처음 도입한 것"이라고 설명했다. 특히 위아래 칩을 접합할 때 전선 대신 미세 실리콘 볼을 사용하는 최첨단 실리콘관통전극(TSV) 기술이 적용돼 데이터 처리 속도와 전력 효율을 높였다.

삼성전자는 이번 성과를 앞세워 파운드리 1위 기업 TSMC 추격에 박차를 가할 방침이다. 원래 7나노 이하 칩 적층 기술 개념은 지난해 TSMC가 처음 제시했지만 실제 개발은 삼성이 먼저 성공한 형국이 됐다. 전세계 파운드리 업계에서 7나노 이하 초미세공정 능력을 갖춘 회사는 이들 2곳뿐으로, 양사는 스마트폰, 개인용컴퓨터(PC), 서버 등 주요 정보기술(IT) 분야의 대형 제조업체들을 고객으로 끌어들이려 치열하게 경쟁하고 있다.

삼성전자는 글로벌 팹리스 고객들이 새 기술을 활용해 5나노 및 7나노 공정 칩을 설계할 수 있도록 엑스큐브 설계툴을 제공하는 한편 이들의 발주에 즉각 응할 수 있는 준비를 갖출 방침이다. 강문수 파운드리 마켓전략팀 전무는 "팹리스 고객이 삼성전자의 생산 인프라를 이용할 경우 개발 오류를 빠르게 확인하고 칩 개발 기간을 줄일 수 있다"고 말했다.

기사 URL이 복사되었습니다.

댓글0